- Сумматор

-

Сумматор — устройство, преобразующее информационные сигналы (аналоговые или цифровые) в сигнал, эквивалентный сумме этих сигналов.[1]

Содержание

История

Подробнее по этой теме см.: История компьтера.См. также: История АВМ- 1623 год и 1624 год — Вильгельм Шиккард в двух письмах Кеплеру описывает считающие часы, в которых одной из трёх главных частей был механический десятичный 6-ти разрядный сумматор[2]

- 1645 год — Паскаль создал механическую суммирующую машину «Паскалину» с механическим десятичным сумматором

- 1673 год — Лейбниц создал механический калькулятор, в котором был механический десятичный сумматор на механическом счётчике

Классификация сумматоров

В зависимости от формы представления информации различают сумматоры аналоговые и цифровые.[1]

По способу реализации

- механические

- электромеханические

- электронные

- пневматические

По принципу действия

- на счётчиках, считающие количества импульсов в операндах

- функциональные, выдающие на выходах значения логической функции суммы по модулю и логической функции разряда переноса:

По архитектуре

- четвертьсумматоры — бинарные (двухоперандные) сумматоры по модулю без разряда переноса, характеризующиеся наличием двух входов, на которые подаются два одноразрядных числа, и одним выходом, на котором реализуется их арифметическая сумма по модулю;[3][неавторитетный источник?][4][неавторитетный источник?]

- полусумматоры — бинарные (двухоперандные) сумматоры по модулю с разрядом переноса, характеризующиеся наличием двух входов, на которые подаются одноимённые разряды двух чисел, и двух выходов: на одном реализуется арифметическая сумма по модулю в данном разряде, а на другом — перенос в следующий (старший разряд);

- полные сумматоры — тринарные (трёхоперандные) сумматоры по модулю с разрядом переноса, характеризующиеся наличием трёх входов, на которые подаются одноимённые разряды двух складываемых чисел и перенос из предыдущего (более младшего) разряда, и двумя выходами: на одном реализуется арифметическая сумма по модулю в данном разряде, а на другом — перенос в следующий (более старший разряд). Такие сумматоры изначально ориентированы только на показательные позиционные системы счисления.

По способу действия

- Последовательные (одноразрядные), в которых обработка разрядов чисел ведётся поочерёдно, разряд за разрядом, на одном и том же одноразрядном оборудовании;

- Параллельные (многоразрядные), в которых слагаемые складываются одновременно по всем разрядам, и для каждого разряда имеется своё оборудование;

По способу организации переноса

- С последовательным переносом;

- С параллельным переносом;

- С условным переносом;

- С групповым переносом.

Двоичный сумматор

Двоичный сумматор может быть определён тремя способами:

1. табличным, в виде таблицы истинности,

2. аналитическим, в виде формулы (СДНФ),

3. графическим, в виде логической схемы.

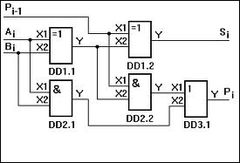

Так как формулы и схемы могут преобразовываться, то, одной таблице истинности двоичного сумматора могут соответствовать множества различных формул и схем. Поэтому, табличный способ определения двоичного сумматора является основным. Рис.1. Логическая схема трёхступенчатого сумматора на двух полусумматорах и логическом элементе 2ИЛИ

Рис.1. Логическая схема трёхступенчатого сумматора на двух полусумматорах и логическом элементе 2ИЛИ

x0=A 1 0 1 0 1 0 1 0 x1=B 1 1 0 0 1 1 0 0 x2=Pi-1 1 1 1 1 0 0 0 0 Название действия (функции) Номер функции Si 1 0 0 1 0 1 1 0 Бит суммы по модулю 2 F3,150 Pi 1 1 1 0 1 0 0 0 Бит переноса F3,232 СДНФ суммы по модулю 2:

СДНФ бита переноса:

Cхема, которая обеспечивает сложение двух однобитных чисел А и В называется полусумматором. Полусумматор имеет 4 сигнальных линии: два входа для сигналов, представляющих одноразрядные двоичные числа А и В, и два выхода: сумма А и В по модулю 2 (S) и сигнал переноса (P). При этом S наименее значимый бит, а P наиболее значимый бит.

Объединив два полусумматора и добавив дополнительную схему ИЛИ, можно создать трёхступенчатый полный сумматор с дополнительным входом Pi-1 (на рисунке 1), который принимает сигнал переноса из предыдущей схемы. Первая ступень на полусумматоре осуществляет сложение двух двоичных чисел и вырабатывает первый частный бит переноса, вторая ступень на полусумматоре осуществляет сложение результата первой ступени с третьим двоичным числом и вырабатывает второй частный бит переноса, третья ступень на логическом элементе 2ИЛИ вырабатывает результирующий бит переноса в старший разряд. Время выполнения операции сложения в сумматоре на рис.1 равно 3dt, где dt - время задержки в одном типовом логическом элементе.

Схема полного сумматора может быть использована в качестве "строительных блоков" для построения схем многоразрядных сумматоров, путём добавления одноразрядных полных сумматоров. Для каждой цифры, которую схема должна быть в состоянии обрабатывать, используется один полный сумматор.

Двоичный одноразрядный полный сумматор является полной тринарной (трёхоперандной) двоичной логической функцией с бинарным (двухразрядным) выходом. Все три операнда и оба выходных разряда однобитные.

Может быть построен как тринарная (трёхоперандная) двоичная логическая функция с бинарным выходом[5] с временем выполнения операции сложения 2dt, но, для уменьшения аппаратных затрат, обычно строится трёхступенчатым, состоящим из трёх узлов: двух полусумматоров, которые являются полными бинарными (двухоперандными) двоичными логическими функциями с унарным выходом и логического элемента «2ИЛИ».

Троичный сумматор

Так как возможно несколько видов физической реализации троичных систем: трёхуровневая однопроводная, двухуровневая двухразрядная двухпроводная, двухуровневая трёхразрядная одноединичная трёхпроводная, двухуровневая трёхразрядная однонулевая и др., то возможны и несколько видов троичных сумматоров.

Кроме этого, сумматоры в несимметричной троичной системе счисления отличаются логикой работы от сумматоров в симметричной троичной системе счисления.

Троичный одноразрядный полный сумматор в троичной несимметричной системе счисления является неполной тринарной (трёхоперандной) троичной логической функцией. Два операнда — два слагаемых — полные, третий операнд — троичный разряд переноса — неполный и имеет только два значения 0 и 1 из трёх.

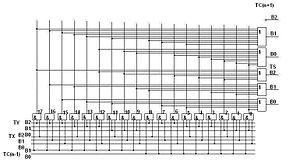

В несимметричной троичной системе счисления

x0 2 1 0 2 1 0 2 1 0 2 1 0 2 1 0 2 1 0 слагаемое x1 2 2 2 1 1 1 0 0 0 2 2 2 1 1 1 0 0 0 слагаемое x2 1 1 1 1 1 1 1 1 1 0 0 0 0 0 0 0 0 0 Перенос из n-1 разряда S 2 1 0 1 0 2 0 2 1 1 0 2 0 2 1 2 1 0 МЗР суммы, сумма по модулю 3 C 1 1 1 1 1 0 1 0 0 1 1 0 1 0 0 0 0 0 СЗР суммы, перенос в n+1 разряд Троичный одноразрядный полный сумматор в трёхбитной одноединичной системе троичных логических элементов, работающий в троичной несимметричной системе счисления, приведённый на рисунке справа описан в [6][неавторитетный источник?].

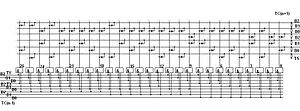

Троичный полный тринарный одноразрядный сумматор, работающий в троичной симметричной системе счисления Фибоначчи, является полной тринарной троичной логической функцией с двухразрядным результатом[7][неавторитетный источник?].

В симметричной троичной системе счисления

x0 1 0 7 1 0 7 1 0 7 1 0 7 1 0 7 1 0 7 1 0 7 1 0 7 1 0 7 слагаемое x1 1 1 1 0 0 0 7 7 7 1 1 1 0 0 0 7 7 7 1 1 1 0 0 0 7 7 7 слагаемое x2 1 1 1 1 1 1 1 1 1 0 0 0 0 0 0 0 0 0 7 7 7 7 7 7 7 7 7 Перенос из n-1 разряда Номер функции S 0 7 1 7 1 0 1 0 7 7 1 0 1 0 7 0 7 1 1 0 7 0 7 1 7 1 0 МЗР суммы F3,-624603703776 C 1 1 0 1 0 0 0 0 0 1 0 0 0 0 0 0 0 7 0 0 0 0 0 7 0 7 7 СЗР суммы (трит переноса в n+1 разряд) F3,3483426737048 "7" обозначает "-1"

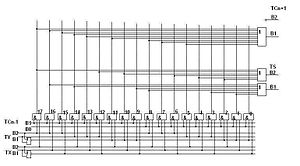

Троичный одноразрядный тринарный (трёхоперандный, полный) сумматор работающий в троичной симметричной системе счисления Фибоначчи в трёхбитной одноединичной системе троичных логических элементов с логическими элементами ИЛИ описан в [8].

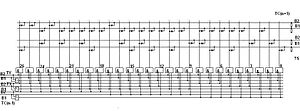

Троичный одноразрядный тринарный (трёхоперандный, полный) сумматор работающий в троичной симметричной системе счисления Фибоначчи в двухбитной системе троичных логических элементов с логическими элементами ИЛИ описан в [9].

Троичный зеркально-симметричный одноразрядный полный сумматор описан в [10]

-

Принципиальная схема одноразрядного сумматора в несимметричной троичной системе счисления в трёхбитной одноединичной системе троичных логических элементов

-

Принципиальная схема троичного одноразрядного сумматора в двухбитной системе троичных логических элементов

-

Принципиальная схема троичного полного одноразрядного сумматора, работающего в троичной симметричной системе счисления Фибоначчи в трёхбитной одноединичной системе троичных логических элементов

-

Принципиальная схема троичного полного сумматора в троичной симметричной системе счисления Фибоначчи в двухбитной системе троичных логических элементов

См. также

- Полусумматор

- Дифференциатор

- Алгебра Буля

- Сложение по модулю 2

- Троичная логика

- Вычитатель

- Схема ускоренного переноса

- АЛУ

Примечания

- ↑ 1 2 Словарь по кибернетике / Под редакцией академика В. С. Михалевича. — 2-е. — Киев: Главная редакция Украинской Советской Энциклопедии имени М. П. Бажана, 1989. — 751 с. — (С48). — 50 000 экз. — ISBN 5-88500-008-5

- ↑ Считающие часы Вильгельма Шиккарда

- ↑ Троичный бинарный (двухоперандный) сумматор по модулю 3 (четвертьсумматор) в троичной несимметричной системе счисления и в троичной симметричной системе счисления с соответствием (0,1,-1)=(0,1,2) в трёхбитной одноединичной системе троичных логических элементов

- ↑ Троичный бинарный сумматор по модулю 3 (четвертьсумматор) в троичной несимметричной системе счисления в трёхбитной одноединичной системе троичных логических элементов

- ↑ А.С.Куликов. Двоичные сумматоры. Быстрый двоичный сумматор

- ↑ Троичный тринарный сумматор в троичной несимметричной системе счисления в трёхбитной системе троичных логических элементов

- ↑ http://andserkul.narod2.ru/troichnie_summatori/ А.С.Куликов. Троичные сумматоры

- ↑ Троичный тринарный сумматор-вычитатель в троичной симметричной системе счисления Фибоначчи в трёхбитной системе троичных логических элементов[неавторитетный источник?]

- ↑ Троичный тринарный сумматор-вычитатель в троичной симметричной системе счисления Фибоначчи в двухбитной системе троичных логических элементов[неавторитетный источник?]

- ↑ Компьютеры Фибоначчи. Троичное зеркально-симметричное сложение и вычитание

Литература

- Угрюмов Е. П. Элементы и узлы ЭЦВМ. М.: Высшая школа, 1976. — 232 с.

- Угрюмов Е. П. Цифровая схемотехника. — СПб.: БХВ-Петербург, 2001. — 528 с.

- Жан М. Рабаи, Ананта Чандракасан, Боривож Николич. 11. Проектирование арифметических блоков: Сумматор // Цифровые интегральные схемы. Методология проектирования = Digital Integrated Circuits. — 2-е изд. — М.: Вильямс, 2007. — С. 912. — ISBN 0-13-090996-3

Ссылки

- Сумматор — статья из Большой советской энциклопедии

- http://slovari.yandex.ru/dict/bse/article/00076/43500.htm Яндекс.Словари: Сумматор

Эту статью следует викифицировать. Пожалуйста, оформите её согласно правилам оформления статей.Категории:- Аналоговые системы

- Компьютерная арифметика

- Электроника

- Математическая логика

Wikimedia Foundation. 2010.